Instruction Set Architecture

Design and Working Instruction Set Architecture

Statement Purpose:

Objective of this lab is to introduce students about 16-bit instruction set architecture. The way it is designed and work. Students will be guided about the way different instructions are formed. Instruction are composed of two main parts: epode and operand. Here, our focus will be on key operations like mov, add, sub, and store. The operands are immediate, register or memory location. Here, we kept the opcode size of 4 bits so that each instruction format supports at max 16 operations. While other 12 bits are kept for the operands.

Activity Outcomes:

This lab teaches you the following topics:

- Students will know that the way 16-bit instruction set architecture is designed and

- Students will be guided about the way different instructions are

- Students will get knowledge of the working of MOV, ADD, SUB and STORE commands in 16 Bit Architecture.

Instructor Note:

Instruction Set Composed of two parts

- Opcode defines the number of operation supported by this instruction format and used for indexing that operation.

- Operands can be immediate value, memory address and register

In our ISA design, the length of instruction is 16 bits. Such that

- 4 bits for opcode

- 12 bits for operand(s)

Operations

- Our focus will be on three operations

- LOADM

- ADDR

- STORER

| OPCODE | Operation |

| 0000 | LOADI |

| 0001 | LOADM |

| 0010 | STOREI |

| 0011 | STORER |

| 0100 | ADDI |

| 0101 | ADDR |

| 0110 | SUBI |

| … | … |

| … | … |

| 1111 | … |

Registers

- There are 16 registers hence 4 bits are required to address them

- Registers are named as R0 to

| Register Address | Register |

| 0000 | R0 |

| 0001 | R1 |

| 0010 | R2 |

| 0011 | R3 |

| 0100 | R4 |

| 0101 | R5 |

| 0110 | R6 |

| … | … |

| … | … |

| 1111 | R15 |

Memory

- There are 28 memory locations where data may Hence 8 bits are required to address them

- Memory locations are named as M0 to

| Memory Address | Memory |

| 00000000 | M0 |

| 00000001 | M1 |

| 00000010 | M2 |

| 00000011 | M3 |

| 00000100 | M4 |

| 00000101 | M5 |

| 00000110 | M6 |

| … | … |

| … | … |

| 11111111 | M255 |

Introduction

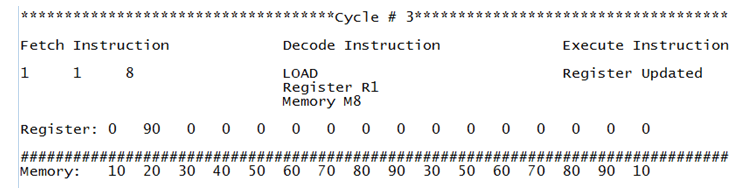

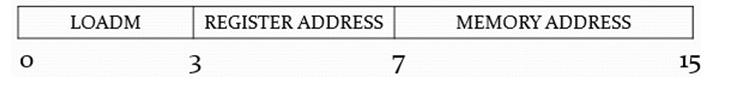

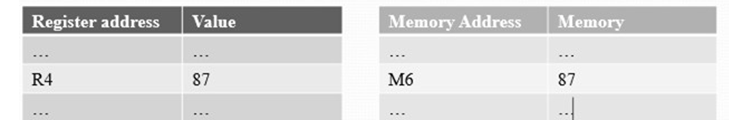

LOADM Instruction:

- Define:

- It loads an operand value from a memory location to a

- Bit allocation:

- bits for Opcode

- 4 bits for Register address

- 8 bits for Memory address

Working

Working

- Consider an example:

Assembly Code: LOADM R4 M6

Machine Code: 0001010000000110

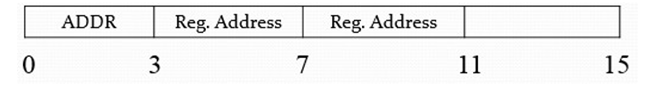

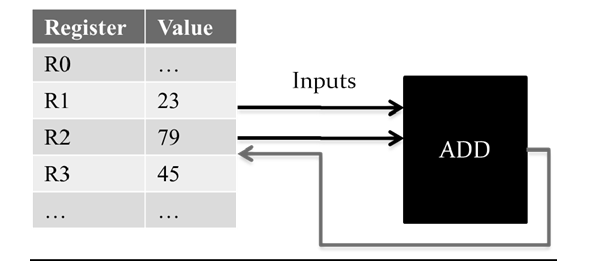

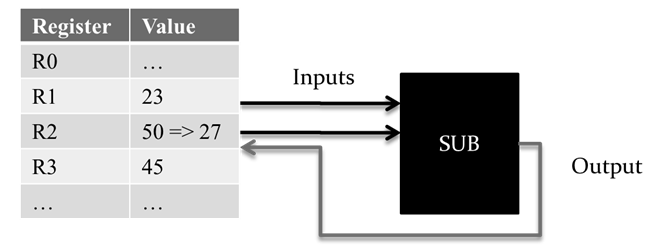

ADDR Instruction:

- Define:

- It adds register values and keeps the result in the destination register.

- Bit allocation:

- 4 bits for Opcode

- 4 bits for each Register address

- 4 bits for Source and 4 bits for Destination

- 4 bits for Source and 4 bits for Destination

Working

Working

Lab Activities:

Activity 1:

Consider the following instruction and provide its working based on the example discussed for LOADM.

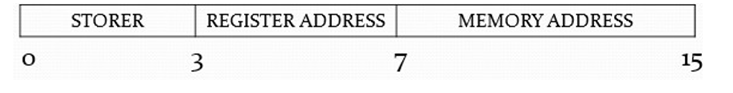

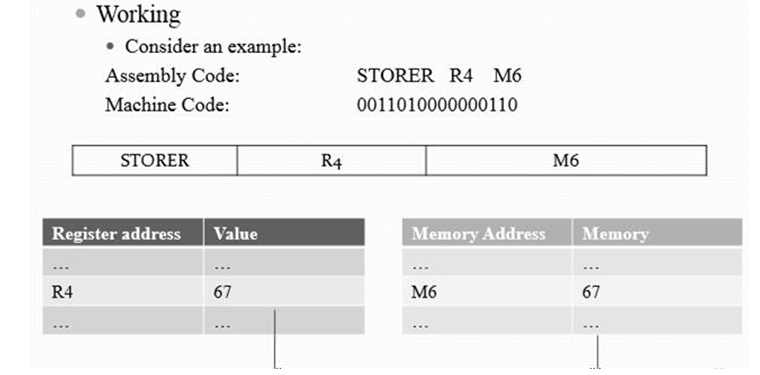

STORER Instruction:

- Define:

- It stores an operand value from a register to a Memory

- Bit allocation:

- bits for Opcode

- 4 bits for Register address

- 8 bits for Memory address

Solution:

Consider the following instruction and provide its working based on the example discussed for ADDR.Activity 2:

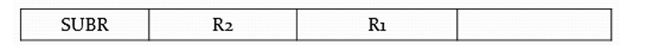

SUBR Instruction:

- Define:

- It subs register values and keeps the result in the destination register.

- Bit allocation:

- 4 bits for Opcode

- 4 bits for each Register address

- 4 bits for Source and 4 bits for Destination

Solution:

Home Activities:

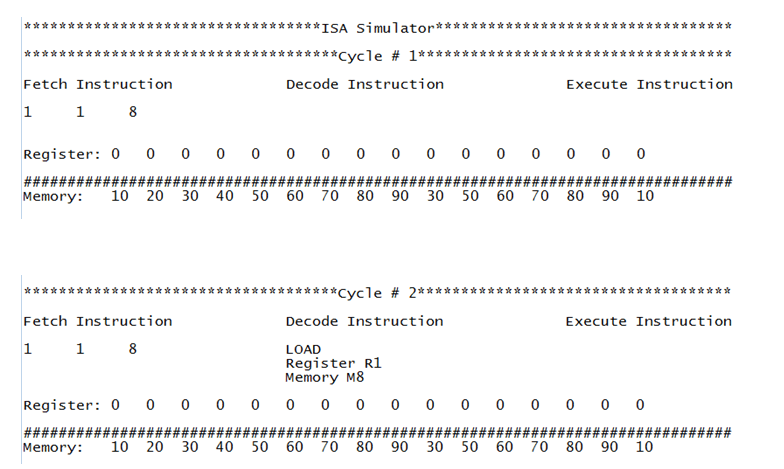

1. Write a simulator for the discussed ISA design in JAVA language.

There should be an input function. It asks for the number of instructions of the program to be executed by simulator. Let suppose user enter 4.

It means there would be two load, one adds and one store instruction for this program.

Input pattern:

- Step 1: Enter Instruction type (Load, Store or Add)

- Step 2: Ask for the operand input according to the

If user selected Load in step 1 then ask for

- Operand # 1: Register Number

- Operand # 2: Memory Address

Ask for the value of memory as well. (Store Memory in SD Array)

Input Test program (4 Instructions)

LOADM R1 M8

LOADM R2 M7

ADDR R2 R1

STORER R2 M8

OR

1 1 8

1 2 7

5 2 1

3 2 8

Execution of the Instruction

- Our CPU will use three stages for executing a single These are

- Fetch: CPU fetches the instruction from Instruction memory (Maintained in a 2D Array)

- Decode: Operation and operands are

- Execute: Operation is performed on the